最近手持ちのARM版WindowsPCが「25H2」にアップデートされたんですが、以前確認したPrismエミュレータに変化があるのか気になったのでさくっと調べるべく早速Coreinfo64.exeを実行してみました。

・・・おお!?なんか変わったぽい!

早速ですがcoreinfo64の出力を公開します。ちなみに前回と同じくWindows Updateは最新の状況にしてありWindows Insider Programには参加していない状況での実行です。

edition : Windows11 Pro

version : 25H2

OS build : 26200.7462

Snapdragon(R) X 10-core X1P64100 @ 3.40 GHz

ARMv8 (64-bit) Family 8 Model 1 Revision 201, Qualcomm Technologies Inc

HTT - Multicore

CET - Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET - User-mode CET Allowed

HYPERVISOR - Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

SVM - Supports AMD hardware-assisted virtualization

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP - Supports Supervisor Mode Execution Prevention

SMAP - Supports Supervisor Mode Access Prevention

PAGE1GB - Supports 1 GB large pages

PAE - Supports > 32-bit physical addresses

PAT - Supports Page Attribute Table

PSE - Supports 4 MB pages

PSE36 - Supports > 32-bit address 4 MB pages

PGE - Supports global bit in page tables

SS - Supports bus snooping for cache operations

VME - Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR - Implements RDMSR/WRMSR instructions

MTRR - Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED - Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX - Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR - Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB - Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE - Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID - Supports PCIDs and settable CR4.PCIDE

INVPCID - Supports INVPCID instruction

PDCM - Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE - Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR - Supports disabling task priority messages

EIST - Supports Enhanced Intel Speedstep

ACPI - Implements MSR for power management

TM - Implements thermal monitor circuitry

TM2 - Implements Thermal Monitor 2 control

APIC - Implements software-accessible local APIC

x2APIC - Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE - Supports Machine Check, INT18 and CR4.MCE

MCA - Implements Machine Check Architecture

PBE - Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

PREFETCHW * Supports PREFETCHW instruction

Maximum implemented CPUID leaves: 0000000D (Basic), 80000008 (Extended).

Maximum implemented address width: 32 bits (virtual), 32 bits (physical).

Processor signature: 00600F01

Logical to Physical Processor Map:

*--------- Physical Processor 0

-*-------- Physical Processor 1

--*------- Physical Processor 2

---*------ Physical Processor 3

----*----- Physical Processor 4

-----*---- Physical Processor 5

------*--- Physical Processor 6

-------*-- Physical Processor 7

--------*- Physical Processor 8

---------* Physical Processor 9

Logical Processor to Socket Map:

********** Socket 0

Logical Processor to NUMA Node Map:

********** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

*--------- Instruction Cache 0, Level 1, 192 KB, Assoc 6, LineSize 64

*--------- Data Cache 0, Level 1, 96 KB, Assoc 6, LineSize 64

****------ Unified Cache 0, Level 2, 12 MB, Assoc 12, LineSize 64

-*-------- Instruction Cache 1, Level 1, 192 KB, Assoc 6, LineSize 64

-*-------- Data Cache 1, Level 1, 96 KB, Assoc 6, LineSize 64

--*------- Instruction Cache 2, Level 1, 192 KB, Assoc 6, LineSize 64

--*------- Data Cache 2, Level 1, 96 KB, Assoc 6, LineSize 64

---*------ Instruction Cache 3, Level 1, 192 KB, Assoc 6, LineSize 64

---*------ Data Cache 3, Level 1, 96 KB, Assoc 6, LineSize 64

----*----- Instruction Cache 4, Level 1, 192 KB, Assoc 6, LineSize 64

----*----- Data Cache 4, Level 1, 96 KB, Assoc 6, LineSize 64

----***--- Unified Cache 1, Level 2, 12 MB, Assoc 12, LineSize 64

-----*---- Instruction Cache 5, Level 1, 192 KB, Assoc 6, LineSize 64

-----*---- Data Cache 5, Level 1, 96 KB, Assoc 6, LineSize 64

------*--- Instruction Cache 6, Level 1, 192 KB, Assoc 6, LineSize 64

------*--- Data Cache 6, Level 1, 96 KB, Assoc 6, LineSize 64

-------*-- Instruction Cache 7, Level 1, 192 KB, Assoc 6, LineSize 64

-------*-- Data Cache 7, Level 1, 96 KB, Assoc 6, LineSize 64

-------*** Unified Cache 2, Level 2, 12 MB, Assoc 12, LineSize 64

--------*- Instruction Cache 8, Level 1, 192 KB, Assoc 6, LineSize 64

--------*- Data Cache 8, Level 1, 96 KB, Assoc 6, LineSize 64

---------* Instruction Cache 9, Level 1, 192 KB, Assoc 6, LineSize 64

---------* Data Cache 9, Level 1, 96 KB, Assoc 6, LineSize 64

Logical Processor to Group Map:

********** Group 0

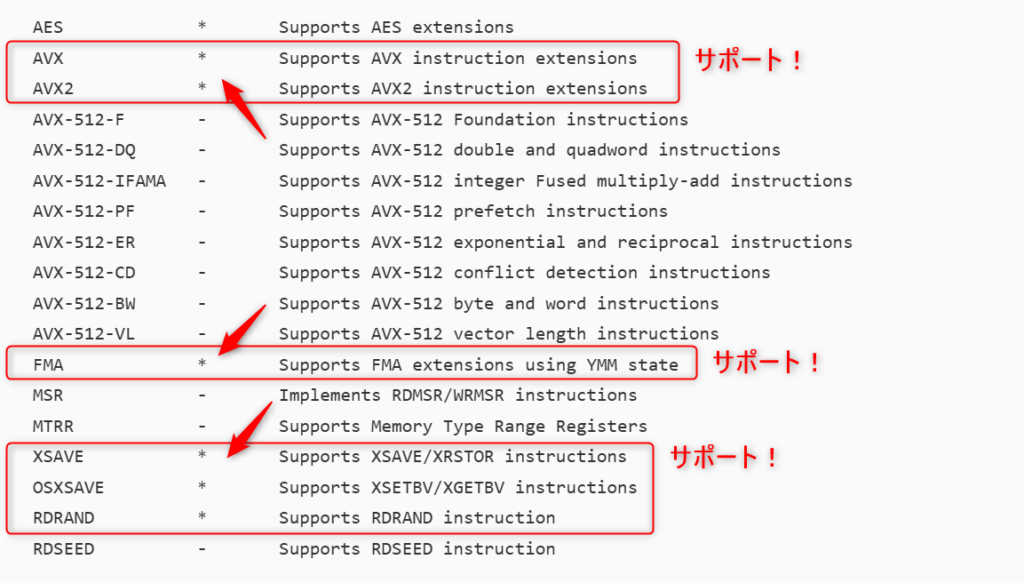

拡張命令 AVX,AVX2 とかが有効化されとる!

いくつかの拡張命令が有効化されてます。どうやら2025年11月プレビューパッチ「KB5070311」で拡張されたようです(出典:窓の杜 Windows on Armのx86/x64エミュ「Prism」がAVX/AVX2命令に対応、いよいよ製品版OSに投入)。他に変更された箇所は無いかチェックしていくと・・・

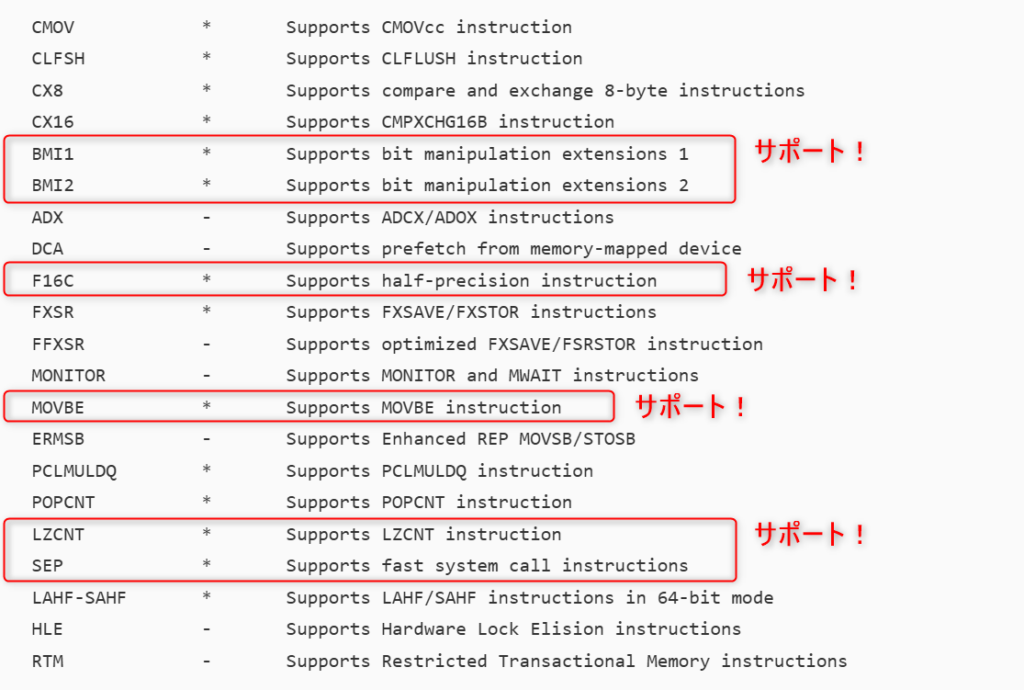

他にも有効化された命令がありました!新たにBMI1、BMI2、F16C、MOVBE、LZCNT、SEPが有効化されているようです。

マイクロソフトからは12月6日に公式ブログ「Windows OS Platform Blog」で紹介されています。記事を読むと今回のアップデートでAVXやAVX2を含むx86命令セットアーキテクチャ拡張やBMI、FMA、F16Cなどの関連拡張をサポートすることで能力を拡大しました、とあります。さらにこれらの拡張機能が提供する効率的な並列処理を活用するクリエイティブツールやゲームにとっては頼られる存在との記述も。なお、今回のアップデートはWindows11のバージョン以降を搭載した全てのWindows on Armデバイスに展開され、全ての64ビットx86アプリはデフォルトでオンになるが、32ビットアプリはデフォルトでオフになるそう。ただし互換性設定で変更可能。

ブログ記事の最後には「我々はWindowsでのPrismエミュレーションを引き続き強化し、今日のアップデートでシームレスに動作する追加アプリやゲームに期待している。」とあります。今後にも期待できそうですね!引き続きウォッチしますよー!

実は結構重要なアプデじゃねえか?これでアプリの互換性は確実に向上してるよな。さて、今後はどこまでサポートを広げるつもりなんやろか・・・